# Maurer Computers for Pipelined Instruction $Processing^{\dagger}$

J. A. BERGSTRA  $^{1,2}$  and C. A. MIDDELBURG  $^{1,\ddagger}$

<sup>1</sup> Programming Research Group, University of Amsterdam, P.O. Box 41882, 1009 DB Amsterdam, the Netherlands; email: J.A.Bergstra@uva.nl, C.A.Middelburg@uva.nl. <sup>2</sup> Department of Philosophy, Utrecht University, P.O. Box 80126, 3508 TC Utrecht, the Netherlands.

Received 13 June 2006; Revised 27 June 2007

We model micro-architectures with non-pipelined instruction processing and pipelined instruction processing, using Maurer machines, basic thread algebra and program algebra. We show that stored programs are executed as intended with these micro-architectures. We believe that this work provides a new mathematical approach to model micro-architectures and to verify their correctness and anticipated speed-up results.

#### 1. Introduction

Pipelined instruction processing is a basic technique used in the design of micro-architectures (see e.g. Hennessy and Patterson (2003) or Sima (2004)). In this paper, we investigate the issue of dealing with pipelined instruction processing when modelling micro-architectures in a mathematically precise way. We model micro-architectures with non-pipelined instruction processing and pipelined instruction processing, using Maurer machines, basic thread algebra and program algebra. Moreover, we show that stored programs are executed as intended with these micro-architectures.

Maurer machines are based on a model for computers proposed in Maurer (1966). Maurer's model for computers is quite different from the well-known models such as register machines, multi-stack machines and Turing machines (see e.g. Hopcroft et al. (2001)). The strength of Maurer's model is that it is close to real computers. The operations that can be performed on the state of a computer play a prominent part in the model. Basic thread algebra is a form of process algebra which is introduced in Bergstra and Loots (2002) under the name basic polarized process algebra. It is a form of process algebra which is tailored to the description of the behaviour of deterministic sequential programs

<sup>&</sup>lt;sup>†</sup> The work presented in this paper has been carried out as part of the GLANCE-project MICROGRIDS, which is funded by the Netherlands Organisation for Scientific Research (NWO).

<sup>&</sup>lt;sup>‡</sup> The work presented in this paper has been partly carried out while the second author was also at Eindhoven University of Technology, Department of Mathematics and Computer Science.

under execution. The behaviours concerned are called threads. Basic thread algebra is used in this paper to direct a Maurer machine in performing operations on its state. Program algebra is introduced in Bergstra and Loots (2002) as well. In program algebra, there is considered, not the behaviour of deterministic sequential programs under execution, but rather the programs themselves. A program is viewed as an instruction sequence. The behaviour of a program is taken for a thread of the kind considered in basic thread algebra. With regard to execution of stored programs on a Maurer machine, we take the line that the programs concerned are programs of the kind considered in program algebra.

To make it possible for threads to direct a Maurer machine in performing operations on its state, basic thread algebra must be extended, for each Maurer machine, with an operator for applying a thread to the Maurer machine from one of its states. Applying a thread to a Maurer machine amounts to generating a sequence of state changes according to the operations that the Maurer machine associates with the basic actions performed by the thread. Because a program is viewed as an instruction sequence in the setting of program algebra, the representation of programs in the memory of a Maurer machine becomes trivial.

Why did we choose to use Maurer machines, basic thread algebra and program algebra to model micro-architectures? First of all, well-known models for computers, such as register machines, multi-stack machines and Turing machines, are too general for our purpose. Unlike Maurer's model for computers, those models have little in common with real computers. For example, a real computer has a memory, and the contents of all memory elements make up the state of the computer. Moreover, a real computer processes instructions, and the processing of an instruction results in changes of the contents of certain memory elements. The design of micro-architectures must deal with these aspects of real computers. Secondly, general process algebras, such as ACP (Bergstra and Klop, 1984; Baeten and Weijland, 1990), CCS (Milner, 1980, 1989), and CSP (Brookes et al., 1984; Hoare, 1985), are too general for our purpose as well. Basic thread algebra has been designed as an algebra of deterministic sequential processes that interact with a machine. In Bergstra and Middelburg (2006b), we show that the processes considered in basic thread algebra can be viewed as processes that are definable over an extension of ACP with conditions introduced in Bergstra and Middelburg (2006a). However, it is quite awkward to describe and analyze processes of this kind using such a general process algebra. Thirdly, there are two reasons to use program algebra: (1) the view that programs are instruction sequences fits in well with real computers, and (2) program behaviours are taken for threads as considered in basic thread algebra.

In Bergstra and Middelburg (2007a), we have demonstrated the feasibility of the microarchitecture modelling approach taken in this paper. In this paper, we make use of the experience gained in that feasibility study to model more advanced micro-architectures. As mentioned above, Maurer's model for computers is quite different from Turing's model. The latter model is part of the foundations of theoretical computer science, whereas the model used in our approach to model micro-architectures is relatively unknown indeed. For that reason, we have investigated the connections between the two models in Bergstra and Middelburg (2007b). We treat the instruction set architecture for which micro-architectures are modelled as a parameter that must fulfil a simple assumption: each instruction from the instruction set must be of a kind considered in program algebra. For example, program algebra considers test instructions and unconditional jump instructions, but it does not consider conditional jump instructions. Besides, program algebra considers forward jump instructions, but it does not consider backward jump instructions. The effect of a conditional jump instruction can be mimicked by a test instruction and an unconditional jump instruction; and the effect of a backward jump instruction can be mimicked by a forward jump instruction because programs may be infinite instruction sequences in program algebra.

In pipelined instruction processing, conditional jump instructions need a treatment different from that of unconditional jump instructions. Backward jump instructions do not need different treatment from that of forward jump instructions in pipelined instruction processing. In order to demonstrate the generality of our approach, we look also in this paper at the influence of extending program algebra with conditional jump instructions on non-pipelined and pipelined instruction processing. We also pay some attention to backward jump instructions.

We do not make explicit the instruction set architecture for which micro-architectures are modelled. In our modelling of a micro-architecture, we start from an arbitrary Maurer machine and enhance it. That Maurer machine determines the instruction set architecture for which a micro-architecture is modelled. However, there are Maurer machines for which the enhancement is primarily intended. We describe in this paper those Maurer machines as well. They are called strict load/store Maurer instruction set architectures.

We regard the work presented in this paper as one of the preparatory steps in developing, as part of a project investigating micro-threading (Bolychevsky et al., 1996; Jesshope and Luo, 2000), a formal approach to design new micro-architectures. That approach should allow for the correctness of new micro-architectures and their anticipated speed-up results to be verified. The work presented in this paper, as well as the preceding work presented in Bergstra and Middelburg (2007a), has convinced us that a special notation for the description of micro-architectures is desirable. However, we found that fixing an appropriate notation still requires some significant design decisions. We come back to this issue in Section 13.

The structure of this paper is as follows. First, we review Maurer computers (Section 2) and basic thread algebra (Section 3). Next, we extend basic thread algebra, for each Maurer machine, with the operator for applying a thread to the Maurer machine from one of its states (Section 4). Following this, we review program algebra (Section 5) and describe the way in which programs are represented in the memory of Maurer machines (Section 6). Then, we model a micro-architecture with non-pipelined instruction processing (Section 7). After that, we model a variant of that micro-architecture with pipelined instruction processing (Sections 8 and 9). Following this, we look at the influence of the addition of conditional jump instructions (Section 10) and briefly discuss the addition of backward jump instructions (Section 11). Then, we describe strict load/store Maurer instruction set architectures (Section 12). Finally, we make some concluding remarks (Section 13).

#### 2. Maurer Computers

In this section, we briefly review Maurer computers, i.e. computers as defined in Maurer (1966).

A Maurer computer C consists of the following components:

```

— a non-empty set M;

```

- a set B with  $card(B) \geq 2$ ;

- a set S of functions  $S: M \to B$ ;

- a set  $\mathcal{O}$  of functions  $O: \mathcal{S} \to \mathcal{S}$ ;

and satisfies the following conditions:

```

— if S_1, S_2 \in \mathcal{S}, M' \subseteq M and S_3 : M \to B is such that S_3(x) = S_1(x) if x \in M' and S_3(x) = S_2(x) if x \notin M', then S_3 \in \mathcal{S};

```

— if

$$S_1, S_2 \in \mathcal{S}$$

, then the set  $\{x \in M \mid S_1(x) \neq S_2(x)\}$  is finite.

M is called the *memory*, B is called the *base set*, the members of S are called the *states*, and the members of O are called the *operations*. It is obvious that the first condition is satisfied if C is *complete*, i.e. if S is the set of all functions  $S: M \to B$ , and that the second condition is satisfied if C is *finite*, i.e. if M and B are finite sets.

In Maurer (1966), operations are called instructions. In the current paper, the term operation is used because of the confusion that would otherwise arise with the instructions of which program algebra programs are made up.

The memory of a Maurer computer consists of memory elements which have as content an element from the base set of the Maurer computer. The contents of all memory elements together make up a state of the Maurer computer. The operations of the Maurer computer transform states in certain ways and thus change the contents of certain memory elements. Thus, a Maurer computer has much in common with a real computer. The first condition on the states of a Maurer computer is a structural condition and the second one is a finite variability condition. We return to these conditions, which are met by any real computer, after the introduction of the input region and output region of an operation.

Let  $(M, B, \mathcal{S}, \mathcal{O})$  be a Maurer computer, and let  $O: \mathcal{S} \to \mathcal{S}$ . Then the *input region* of O, written IR(O), and the *output region* of O, written OR(O), are the subsets of M defined as follows:

$$IR(O) = \left\{ x \in M \mid \exists S_1, S_2 \in \mathcal{S} \cdot (\forall z \in M \setminus \{x\} \cdot S_1(z) = S_2(z) \land \exists y \in OR(O) \cdot O(S_1)(y) \neq O(S_2)(y)) \right\},$$

$$OR(O) = \left\{ x \in M \mid \exists S \in \mathcal{S} \cdot S(x) \neq O(S)(x) \right\}.^{\dagger}$$

OR(O) is the set of all memory elements that are possibly affected by O; and IR(O) is the set of all memory elements that possibly affect elements of OR(O) under O.

Let  $(M, B, \mathcal{S}, \mathcal{O})$  be a Maurer computer, let  $S_1, S_2 \in \mathcal{S}$ , and let  $O \in \mathcal{O}$ . Then  $S_1 \upharpoonright$

<sup>&</sup>lt;sup>†</sup> The following precedence conventions are used in logical formulas. Operators bind stronger than predicate symbols, and predicate symbols bind stronger than logical connectives and quantifiers. Moreover,  $\neg$  binds stronger than  $\land$  and  $\lor$ , and  $\land$  and  $\lor$  bind stronger than  $\Rightarrow$  and  $\Leftrightarrow$ . Quantifiers are given the smallest possible scope.

$IR(O) = S_2 \upharpoonright IR(O)$  implies  $O(S_1) \upharpoonright OR(O) = O(S_2) \upharpoonright OR(O)$ . In other words, every operation transforms states that coincide on the input region of the operation to states that coincide on the output region of the operation. The second condition on the states of a Maurer computer is necessary for this fundamental property to hold. The first condition on the states of a Maurer computer could be relaxed somewhat.

Let  $(M, B, \mathcal{S}, \mathcal{O})$  be a Maurer computer, let  $O \in \mathcal{O}$ , let  $M' \subseteq OR(O)$ , and let  $M'' \subseteq IR(O)$ . Then the region affecting M' under O, written RA(M', O), and the region affected by M'' under O, written AR(M'', O), are the subsets of M defined as follows:

$$RA(M',O) = \left\{ x \in IR(O) \mid AR(\{x\},O) \cap M' \neq \emptyset \right\},$$

$$AR(M'',O) = \left\{ x \in OR(O) \mid \exists S_1, S_2 \in \mathcal{S} \cdot (\forall z \in IR(O) \setminus M'' \cdot S_1(z) = S_2(z) \land O(S_1)(x) \neq O(S_2)(x)) \right\}.$$

AR(M'', O) is the set of all elements of OR(O) that are possibly affected by the elements of M'' under O; and RA(M', O) is the set of all elements of IR(O) that possibly affect elements of M' under O.

In Maurer (1966), Maurer gives many results about the relation between the input region and output region of operations, the composition of operations, the decomposition of operations and the existence of operations with specified input, output and affected regions. In Bergstra and Middelburg (2007a), we summarize the main results. Recently, a revised and expanded version of Maurer (1966), which includes all the proofs, has appeared in Maurer (2006).

## 3. Basic Thread Algebra

In this section, we review BTA (Basic Thread Algebra), a form of process algebra which is tailored to the description of the behaviour of deterministic sequential programs under execution. The behaviours concerned are called *threads*.

In BTA, it is assumed that there is a fixed but arbitrary set of *basic actions*  $\mathcal{A}$  with  $tau \notin \mathcal{A}$ . We write  $\mathcal{A}_{tau}$  for  $\mathcal{A} \cup \{tau\}$ . BTA has the following constants and operators:

- the deadlock constant D;

- the *termination* constant S;

- for each  $a \in \mathcal{A}_{\mathsf{tau}}$ , a binary postconditional composition operator  $\_ \subseteq a \trianglerighteq \_$ .

We use infix notation for postconditional composition. We introduce *action prefixing* as an abbreviation:  $a \circ p$ , where p is a term of BTA, abbreviates  $p \subseteq a \supseteq p$ .

The intuition is that each basic action performed by a thread is taken as a command to be processed by the execution environment of the thread. The processing of a command may involve a change of state of the execution environment. At completion of the processing of the command, the execution environment produces a reply value. This reply is either  $\mathsf{T}$  or  $\mathsf{F}$  and is returned to the thread concerned. Let p and q be closed terms of

<sup>&</sup>lt;sup>‡</sup> We use the notation f D, where f is a function and  $D \subseteq \text{dom}(f)$ , for the function g with dom(g) = D such that for all  $d \in \text{dom}(g)$ , g(d) = f(d).

Table 1. Axiom of BTA

$x \unlhd \mathsf{tau} \,{\trianglerighteq}\, y = x \unlhd \mathsf{tau} \,{\trianglerighteq}\, x \quad \mathrm{T}1$

Table 2. Axioms for guarded recursion

$$\begin{split} \langle X|E\rangle &= \langle t_X|E\rangle & \text{ if } X \!=\! t_X \in E \quad \text{RDP} \\ E \, \Rightarrow \, X &= \langle X|E\rangle & \text{ if } X \in \mathcal{V}(E) & \text{RSP} \end{split}$$

BTA. Then  $p \le a \ge q$  will perform action a, and after that proceed as p if the processing of a leads to the reply T (called a positive reply) and proceed as q if the processing of a leads to the reply F (called a negative reply). The action tau plays a special role. Its execution will never change any state and always produces a positive reply.

BTA has only one axiom. This axiom is given in Table 1. Using the abbreviation introduced above, axiom T1 can be written as follows:  $x \le tau \ge y = tau \circ x$ .

A recursive specification over BTA is a set of equations  $E = \{X = t_X \mid X \in V\}$ , where V is a set of variables and each  $t_X$  is a term of BTA that contains only variables from V. We write V(E) for the set of all variables that occur on the left-hand side of an equation in E. Let t be a term of BTA containing a variable X. Then an occurrence of X in t is guarded if t has a subterm of the form  $t' \leq a \geq t''$  containing this occurrence of X. A recursive specification E is guarded if all occurrences of variables in the right-hand sides of its equations are guarded or it can be rewritten to such a recursive specification using the equations of E. We are only interested in models of BTA in which guarded recursive specifications have unique solutions, such as the projective limit model of BTA presented in Bergstra and Bethke (2003). A thread that is the solution of a finite guarded recursive specification over BTA is called a finite-state thread.

We extend BTA with guarded recursion by adding constants for solutions of guarded recursive specifications and axioms concerning these additional constants. For each guarded recursive specification E and each  $X \in V(E)$ , we add a constant standing for the unique solution of E for X to the constants of BTA. The constant standing for the unique solution of E for X is denoted by  $\langle X|E\rangle$ . Moreover, we use the following notation. Let t be a term of BTA and E be a guarded recursive specification. Then we write  $\langle t|E\rangle$  for t with, for all  $X \in V(E)$ , all occurrences of X in t replaced by  $\langle X|E\rangle$ . We add the axioms for guarded recursion given in Table 2 to the axioms of BTA. In this table, X,  $t_X$  and E stand for an arbitrary variable, an arbitrary term of BTA and an arbitrary guarded recursive specification, respectively. Side conditions are added to restrict the variables, terms and guarded recursive specifications for which X,  $t_X$  and E stand. The additional axioms for guarded recursion are known as the recursive definition principle (RDP) and the recursive specification principle (RSP). The equations  $\langle X|E\rangle = \langle t_X|E\rangle$  for a fixed E express that the constants  $\langle X|E\rangle$  make up a solution of E. The conditional equations  $E \Rightarrow X = \langle X|E\rangle$  express that this solution is the only one.

We often write X for  $\langle X|E\rangle$  if E is clear from the context. It should be borne in mind that, in such cases, we use X as a constant.

The projective limit characterization of process equivalence on threads is based on the

Table 3. Approximation induction principle

$$\bigwedge_{n\geq 0} \pi_n(x) = \pi_n(y) \Rightarrow x = y$$

AIP

Table 4. Axioms for projection operators

| P0 |

|----|

| P1 |

| P2 |

| P3 |

|    |

notion of a finite approximation of depth n. When for all n these approximations are identical for two given threads, both threads are considered identical. This is expressed by the infinitary conditional equation AIP (Approximation Induction Principle) given in Table 3. Here, following Bergstra and Bethke (2003), approximation of depth n is phrased in terms of a unary projection operator  $\pi_n(_{-})$ . The projection operators are defined inductively by means of the axioms given in Table 4. In this table, a stands for an arbitrary member of  $\mathcal{A}_{\text{tau}}$ . It happens that RSP follows from AIP.

The structural operational semantics of BTA and its extensions with guarded recursion and projection can be found in Bergstra and Middelburg (2005) and Bergstra and Middelburg (2007a).

Henceforth, we write  $\mathcal{T}_{\text{finrec}}$  for the set of all closed terms of BTA with guarded recursion in which no constants  $\langle X|E\rangle$  for infinite E occur. We write  $\mathcal{T}_{\text{finrec}}(A)$ , where  $A\subseteq\mathcal{A}$ , for the set of all closed terms from  $\mathcal{T}_{\text{finrec}}$  that contain only basic actions from A.

## 4. Applying Threads to Maurer Machines

In this section, we introduce Maurer machines and add for each Maurer machine H a binary apply operator  $\_\bullet_H \_$  to BTA.

A Maurer machine is a tuple  $H = (M, B, \mathcal{S}, \mathcal{O}, A, \llbracket - \rrbracket)$ , where  $(M, B, \mathcal{S}, \mathcal{O})$  is a Maurer computer and:

The members of A are called the *basic actions* of H, and  $\llbracket \_ \rrbracket$  is called the *basic action interpretation function* of H. A and  $\llbracket \_ \rrbracket$  constitute the interface between the Maurer computer and its environment.

The apply operators associated with Maurer machines are related to the apply operators introduced in Bergstra and Ponse (2002). They allow for threads to transform states of the associated Maurer machine by means of its operations. Such state transformations produce either a state of the associated Maurer machine or the *undefined state*  $\uparrow$ . It is

<sup>§</sup> Let  $A_1, \ldots, A_n$  be sets. Then the function from  $A_1 \times \ldots \times A_n$  to  $A_i$  ( $1 \le i \le n$ ) which maps each  $(a_1, \ldots, a_n) \in A_1 \times \ldots \times A_n$  to  $a_i$  is usually denoted by  $\pi_i$ . We write  $\mathfrak{p}_i$  instead of  $\pi_i$  because of the confusion that would otherwise arise with the projection operator introduced in Section 3.

8

Table 5. Defining equations for apply operator

```

\begin{array}{c} x \bullet_{H} \uparrow = \uparrow \\ \mathsf{S} \bullet_{H} S = S \\ \mathsf{D} \bullet_{H} S = \uparrow \\ (\mathsf{tau} \circ x) \bullet_{H} S = x \bullet_{H} S \\ (x \unlhd a \unrhd y) \bullet_{H} S = x \bullet_{H} O_{a}(S) \text{ if } O_{a}(S)(m_{a}) = \mathsf{T} \\ (x \unlhd a \unrhd y) \bullet_{H} S = y \bullet_{H} O_{a}(S) \text{ if } O_{a}(S)(m_{a}) = \mathsf{F} \end{array}

```

Table 6. Rule for divergence

```

\bigwedge_{n>0} \pi_n(x) \bullet_H S = \uparrow \Rightarrow x \bullet_H S = \uparrow

```

assumed that  $\uparrow$  is not a state of any Maurer machine. We extend function restriction to  $\uparrow$  by stipulating that  $\uparrow \uparrow M = \uparrow$  for any set M. The first operand of the apply operator  $\_ \bullet_{H \_}$  associated with Maurer machine  $H = (M, B, \mathcal{S}, \mathcal{O}, A, \llbracket\_\rrbracket)$  must be a term from  $\mathcal{T}_{\mathsf{finrec}}(A)$  and its second argument must be a state from  $\mathcal{S} \cup \{\uparrow\}$ .

Let  $H = (M, B, \mathcal{S}, \mathcal{O}, A, \llbracket \_ \rrbracket)$  be a Maurer machine, let  $p \in \mathcal{T}_{\mathsf{finrec}}(A)$ , and let  $S \in \mathcal{S}$ . Then  $p \bullet_H S$  is the state that results if all basic actions performed by thread p are processed by the Maurer machine H from initial state S. Moreover, let  $(O_a, m_a) = \llbracket a \rrbracket$  for all  $a \in A$ . Then the processing of a basic action a by H amounts to a state change according to the operation  $O_a$ . In the resulting state, the reply produced by H is contained in memory element  $m_a$ . If p is S, then there will be no state change. If p is D, then the result is  $\uparrow$ .

Let  $H = (M, B, \mathcal{S}, \mathcal{O}, A, \llbracket - \rrbracket)$  be a Maurer machine, and let  $(O_a, m_a) = \llbracket a \rrbracket$  for all  $a \in A$ . Then the apply operator  $\_ \bullet_{H -}$  is defined by the equations given in Table 5 and the rule given in Table 6. In these tables, a stands for an arbitrary member of A and S stands for an arbitrary member of S.

Let  $H = (M, B, \mathcal{S}, \mathcal{O}, A, \llbracket \_ \rrbracket)$  be a Maurer machine, let  $p \in \mathcal{T}_{\mathsf{finrec}}(A)$ , and let  $S \in \mathcal{S}$ . Then p converges from S on H if there exists an  $n \in \mathbb{N}$  such that  $\pi_n(p) \bullet_H S \neq \uparrow$ . We say that p diverges from S on H if p does not converge from S on H. The rule from Table 6 can be read as follows: if x diverges from S on H, then  $x \bullet_H S$  equals  $\uparrow$ .

We introduce some auxiliary notions, which are useful in proofs to come.

Let  $H = (M, B, \mathcal{S}, \mathcal{O}, A, \llbracket \_ \rrbracket)$  be a Maurer machine, and let  $(O_a, m_a) = \llbracket a \rrbracket$  for all  $a \in A$ . Then the step relation  $\_ \vdash_{H} \_ \subseteq (\mathcal{T}_{\mathsf{finrec}}(A) \times \mathcal{S}) \times (\mathcal{T}_{\mathsf{finrec}}(A) \times \mathcal{S})$  is inductively defined as follows:

```

\begin{split} & - \text{if } p = \mathsf{tau} \circ p', \text{ then } (p,S) \vdash_H (p',S); \\ & - \text{if } O_a(S)(m_a) = \mathsf{T} \text{ and } p = p' \unlhd a \trianglerighteq p'', \text{ then } (p,S) \vdash_H (p',O_a(S)); \\ & - \text{if } O_a(S)(m_a) = \mathsf{F} \text{ and } p = p' \unlhd a \trianglerighteq p'', \text{ then } (p,S) \vdash_H (p'',O_a(S)). \end{split}

```

Let  $H=(M,B,\mathcal{S},\mathcal{O},A,\llbracket \_\rrbracket)$  be a Maurer machine. Then a full path in  $\_ \vdash_H \_$  is one of the following:

```

— a finite path \langle (p_0, S_0), \dots, (p_n, S_n) \rangle in \_\vdash_H \_ such that there exists no (p_{n+1}, S_{n+1}) \in \mathcal{T}_{\mathsf{finrec}}(A) \times \mathcal{S} with (p_n, S_n) \vdash_H (p_{n+1}, S_{n+1});

— an infinite path \langle (p_0, S_0), (p_1, S_1), \dots \rangle in \_\vdash_H \_.

```

Moreover, let  $p \in \mathcal{T}_{\mathsf{finrec}}(A)$ , and let  $S \in \mathcal{S}$ . Then the full path of (p, S) on H is the unique

full path in  $\_\vdash_H \_$  from (p,S). If p converges from S on H, then the full path of (p,S) on H is called the *computation* of (p,S) on H and we write  $\|(p,S)\|_H$  for the length of the computation of (p,S) on H.

It is easy to see that  $(p_0, S_0) \vdash_H (p_1, S_1)$  only if  $p_0 \bullet_H S_0 = p_1 \bullet_H S_1$  and that  $\langle (p_0, S_0), \dots, (p_n, S_n) \rangle$  is the computation of  $(p_0, S_0)$  on H only if  $p_n = S$  and  $S_n = p_0 \bullet_H S_0$ . It is also easy to see that, if  $p_0$  converges from  $S_0$  on H,  $\|(p_0, S_0)\|_H$  is the least  $n \in \mathbb{N}$  such that  $\pi_n(p_0) \bullet_H S_0 \neq \uparrow$ .

In the definition of a Maurer machine, we could have taken a function  $\llbracket \_ \rrbracket$  that associates with each  $a \in A$  a triple  $(n_a, O_a, m_a) \in M \times \mathcal{O} \times M$  such that  $S(n_a), S(m_a) \in \{\mathsf{T}, \mathsf{F}\}$  for all  $S \in \mathcal{S}$ . In that case,  $S(n_a)$  would indicate whether basic action a is enabled in state S, i.e. whether the processing of a is not blocked in state S. In this paper, we consider only threads that are behaviours of deterministic sequential programs under execution. For such behaviours, it is not at all interesting to take into account the possibility that some basic actions are not always enabled. Therefore, it is assumed that all basic actions of a Maurer machine are enabled in all states. Under this assumption, it is sufficient that the function  $\llbracket \_ \rrbracket$  associates with each  $a \in A$  a pair  $(O_a, m_a) \in \mathcal{O} \times M$  as in the definition given at the beginning of this section.

#### 5. Program Algebra

In this section, we review PGA (ProGram Algebra), an algebra of sequential programs based on the idea that sequential programs are in essence sequences of instructions. PGA provides a program notation for finite-state threads. A hierarchy of program notations that provide more and more sophisticated programming features are rooted in PGA (see Bergstra and Loots (2002)).

In PGA, it is assumed that there is a fixed but arbitrary set  $\mathfrak A$  of basic instructions. PGA has the following primitive instructions:

- for each  $a \in \mathfrak{A}$ , a void basic instruction a;

- for each  $a \in \mathfrak{A}$ , a positive test instruction +a;

- for each  $a \in \mathfrak{A}$ , a negative test instruction -a;

- for each  $k \in \mathbb{N}$ , a forward jump instruction #k;

- a termination instruction!.

We write  $\Im$  for the set of all primitive instructions.

The intuition is that the execution of a basic instruction a may modify a state and produces T or F at its completion. In the case of a positive test instruction +a, basic instruction a is executed and execution proceeds with the next primitive instruction if T is produced and otherwise the next primitive instruction is skipped and execution proceeds with the primitive instruction following the skipped one. In the case where T is produced and there is not at least one subsequent primitive instruction and in the case where F is produced and there are not at least two subsequent primitive instructions, deadlock occurs. In the case of a negative test instruction -a, the role of the value produced is reversed. In the case of a void basic instruction a, the value produced is disregarded: execution always proceeds as if T is produced. The effect of a forward jump instruction

10

Table 7. Axioms of PGA

```

\begin{array}{ll} (X\,;Y)\,;Z=X\,;(Y\,;Z) & \mathrm{PGA1} \\ (X^n)^\omega = X^\omega & \mathrm{PGA2} \\ X^\omega\,;Y=X^\omega & \mathrm{PGA3} \\ (X\,;Y)^\omega = X\,;(Y\,;X)^\omega & \mathrm{PGA4} \end{array}

```

Table 8. Defining equations for thread extraction operator

```

\begin{array}{ll} |a| = a \circ \mathsf{D} & |\#k| = \mathsf{D} \\ |a\,;\, X| = a \circ |X| & |\#0\,;\, X| = \mathsf{D} \\ |+a| = a \circ \mathsf{D} & |\#1\,;\, X| = |X| \\ |+a\,;\, X| = |X| \unlhd a \trianglerighteq |\#2\,;\, X| & |\#k+2\,;\, u| = \mathsf{D} \\ |-a| = a \circ \mathsf{D} & |\#k+2\,;\, u\,;\, X| = |\#k+1\,;\, X| \\ |-a\,;\, X| = |\#2\,;\, X| \unlhd a \trianglerighteq |X| & |!\,| = \mathsf{S} \\ |!\,;\, X| = \mathsf{S} \end{array}

```

#k is that execution proceeds with the kth next instruction of the program concerned. If k equals 0 or the kth next instruction does not exist, then #k results in deadlock. The effect of the termination instruction! is that execution terminates.

The thread extraction operator introduced below, together with the apply operators introduced in Section 4, makes it possible to associate operations of Maurer machines with basic instructions, and consequently with primitive instructions of PGA.

PGA has the following constants and operators:

- for each  $u \in \mathfrak{I}$ , an instruction constant u;

- the binary concatenation operator \_ ; \_ ;

- the unary repetition operator  $_{-}^{\omega}$ .

Closed terms of PGA are considered to denote programs. The intuition is that a program is in essence a non-empty finite or infinite sequence of primitive instructions. These sequences are called single pass instruction sequences because PGA has been designed to enable single pass execution of instruction sequences: each instruction can be dropped after it has been executed. Programs are considered to be equal if they represent the same single pass instruction sequence. The axioms for instruction sequence equivalence are given in Table 7. In this table, n stands for an arbitrary natural number greater than 0. For each n>0, the term  $X^n$  is defined by induction on n as follows:  $X^1=X$  and  $X^{n+1}=X$ ;  $X^n$ . The unfolding equation  $X^\omega=X$ ;  $X^\omega$  is derivable. Each closed term of PGA is derivably equal to a term in canonical form, i.e. a term of the form P or P;  $Q^\omega$ , where P and Q are closed terms of PGA that do not contain the repetition operator.

Each closed term of PGA is considered to denote a program of which the behaviour is a finite-state thread, taking the set  $\mathfrak A$  of basic instructions for the set  $\mathcal A$  of actions. The thread extraction operator |-| assigns a thread to each program. The thread extraction operator is defined by the equations given in Table 8 (for  $a \in \mathfrak A$ ,  $k \in \mathbb N$  and  $u \in \mathfrak I$ ) and the rule given in Table 9. This rule is expressed in terms of the structural congruence predicate  $_{-}\cong$  \_\_, which is defined by the formulas given in Table 10 (for  $n, m, k \in \mathbb N$  and  $u_1, \ldots, u_n, v_1, \ldots, v_{m+1} \in \mathfrak I$ ).

```

Table 9. Rule for cyclic jump chains

```

```

X\cong \#0\,;Y\,\Rightarrow\,|X|=\mathsf{D}

```

Table 10. Defining formulas for structural congruence predicate

```

\begin{split} \#n+1\,;\,u_1\,;\,\ldots\,;\,u_n\,;\,\#0&\cong\#0\,;\,u_1\,;\,\ldots\,;\,u_n\,;\,\#0\\ \#n+1\,;\,u_1\,;\,\ldots\,;\,u_n\,;\,\#m&\cong\#m+n+1\,;\,u_1\,;\,\ldots\,;\,u_n\,;\,\#m\\ (\#n+k+1\,;\,u_1\,;\,\ldots\,;\,u_n)^\omega&\cong(\#k\,;\,u_1\,;\,\ldots\,;\,u_n)^\omega\\ \#m+n+k+2\,;\,u_1\,;\,\ldots\,;\,u_n\,;\,(v_1\,;\,\ldots\,;\,v_{m+1})^\omega&\cong\\ &\qquad\qquad\qquad \#n+k+1\,;\,u_1\,;\,\ldots\,;\,u_n\,;\,(v_1\,;\,\ldots\,;\,v_{m+1})^\omega\\ X&\cong X\\ X_1&\cong Y_1\wedge X_2\cong Y_2\,\Rightarrow\,X_1\,;\,X_2\cong Y_1\,;\,Y_2\wedge X_1^\omega\cong Y_1^\omega \end{split}

```

The equations given in Table 8 do not cover the case where there is a cyclic chain of forward jumps. Programs are structurally congruent if they are the same after removing all chains of forward jumps in favour of direct jumps. Because a cyclic chain of forward jumps corresponds to #0, the rule from Table 9 can be read as follows: if X starts with a cyclic chain of forward jumps, then |X| equals D. It is easy to see that the thread extraction operator assigns the same thread to structurally congruent programs. Therefore, the rule from Table 9 can be replaced by the following generalization:  $X \cong Y \Rightarrow |X| = |Y|$ .

Let E be a finite guarded recursive specification over BTA, and let  $P_X$  be a closed term of PGA for each  $X \in V(E)$ . Let E' be the set of equations that results from replacing in E all occurrences of X by  $|P_X|$  for each  $X \in V(E)$ . If E' can be obtained by applications of axioms PGA1–PGA4, the defining equations for the thread extraction operator, and the rule for cyclic jump chains, then  $|P_X|$  is the solution of E for X. Such a finite guarded recursive specification can always be found. Thus, the behaviour of each closed PGA term is a thread that is definable by a finite guarded recursive specification over BTA. Moreover, each finite guarded recursive specification over BTA can be translated to a PGA program of which the behaviour is the solution of the finite guarded recursive specification concerned.

Closed terms of PGA are loosely called PGA programs. PGA programs in which the repetition operator does not occur are called *finite* PGA programs. Henceforth, we write  $\mathcal{P}_{\mathsf{fin}}$  for the set of all finite PGA programs. We write  $\mathcal{P}_{\mathsf{fin}}(A)$ , where  $A \subseteq \mathfrak{A}$ , for the set of all closed terms from  $\mathcal{P}_{\mathsf{fin}}$  that contain only basic instructions from A.

In the remainder of this paper, with the exception of Section 11, we consider only finite PGA programs.

#### 6. Stored Programs

In this short section, we make precise how to represent PGA programs in the memory of a Maurer machine.

It is assumed that a fixed but arbitrary finite set  $M_{prog}$  and a fixed but arbitrary bijection  $m_{prog}$ :  $[0, card(M_{prog}) - 1] \rightarrow M_{prog}$  have been given.  $M_{prog}$  is called the *program*

memory. We write  $size(\mathsf{M}_{\mathsf{prog}})$  for  $card(\mathsf{M}_{\mathsf{prog}})$ . Let  $n, n' \in [0, size(\mathsf{M}_{\mathsf{prog}}) - 1]$  be such that  $n \leq n'$ . Then, we write  $\mathsf{M}_{\mathsf{prog}}[n]$  for  $\mathsf{m}_{\mathsf{prog}}(n)$ , and  $\mathsf{M}_{\mathsf{prog}}[n, n']$  for  $\{\mathsf{m}_{\mathsf{prog}}(k) \mid n \leq k \leq n'\}$ .

The program memory is a memory of which the elements can be addressed by means of members of  $[0, size(\mathsf{M}_{\mathsf{prog}}) - 1]$ . We write  $\mathsf{MA}_{\mathsf{prog}}$  for  $[0, size(\mathsf{M}_{\mathsf{prog}}) - 1]$  and  $\mathsf{MA}'_{\mathsf{prog}}$  for  $[0, size(\mathsf{M}_{\mathsf{prog}})]$ .

The program memory elements are meant to contain the primitive instructions that form part of a finite PGA program.

We write  $\mathfrak{I}_{prog}$  for  $\mathfrak{I} \setminus \{\#k \mid k > size(\mathsf{M}_{prog}) - 1\}$ .  $\mathfrak{I}_{prog}$  is the program memory base set. We write  $\mathsf{S}_{prog}$  for the set of all functions  $S_{prog} : \mathsf{M}_{prog} \to \mathfrak{I}_{prog}$ .

Let  $P = u_1$ ; ...;  $u_n \in \mathcal{P}_{\mathsf{fin}}$  with  $n \leq \mathit{size}(\mathsf{M}_{\mathsf{prog}})$ . Then the stored representation of P, written  $\mathsf{s}_{\mathsf{prog}}(P)$ , is the unique function  $s_{\mathsf{prog}} : \mathsf{M}_{\mathsf{prog}}[0, n-1] \to \mathfrak{I}_{\mathsf{prog}}$  such that for all  $i \in [0, n-1]$ ,  $s_{\mathsf{prog}}(\mathsf{M}_{\mathsf{prog}}[i]) = u_{i+1}$ . We call  $\mathsf{s}_{\mathsf{prog}}(P)$  a stored program.

Note that  $s_{prog}(u_1; ...; u_n)$  is not defined if  $n > size(M_{prog})$ . The size of the program memory restricts the programs that can be stored.

## 7. Non-Pipelined Instruction Processing

In this section, we model a micro-architecture with non-pipelined instruction processing. We do not make the instruction set architecture for which this micro-architecture is modelled explicit. We start from an arbitrary Maurer machine and enhance it. That Maurer machine determines the instruction set architecture for which a micro-architecture is modelled. However, there are Maurer machines for which the enhancement is primarily intended. Those Maurer machines will be introduced in Section 12. Henceforth, we write "PGA instruction" for "primitive instruction of PGA".

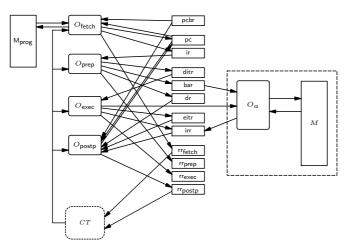

We enhance Maurer machines by extending the memory with a program memory (M<sub>prog</sub>), a program counter upper bound register (pcbr), a program counter (pc), an instruction register (ir), a decoded instruction type register (ditr), a basic action register (bar), a displacement register (dr), an executed instruction type register (eitr), an instruction reply register (irr), a fetch reply register (rrfetch), a pre-process reply register (rr<sub>prep</sub>), an execute reply register (rr<sub>exec</sub>) and a post-process reply register (rr<sub>postp</sub>), and the operation set with a fetch operation  $(O_{\text{fetch}})$ , a pre-process operation  $(O_{\text{prep}})$ , an execute operation  $(O_{\text{exec}})$  and a post-process operation  $(O_{\text{postp}})$ . Moreover, we replace the basic actions of the original Maurer machine by basic actions fetch, prep, exec and postp, with which the operations  $O_{\text{fetch}}$ ,  $O_{\text{prep}}$ ,  $O_{\text{exec}}$  and  $O_{\text{postp}}$  are associated. The resulting Maurer machines are called SP-NPL-enhancements. SP stands for stored program and NPL stands for non-pipelined instruction processing. In SP-NPL-enhancements of Maurer machines, the five instruction types bsc, ptst, ntst, fjmp and term are distinguished. These types correspond to the five kinds of PGA instructions introduced in Section 5. Henceforth, we write IT for the set {bsc, ptst, ntst, fjmp, term}. The memory elements pcbr, pc, ir, ditr, bar, dr, eitr and irr are used to communicate information between the execution handling operations  $O_{\text{fetch}}$ ,  $O_{\text{prep}}$ ,  $O_{\text{exec}}$  and  $O_{\text{postp}}$ . The memory elements  $\text{rr}_{\text{fetch}}$ ,  $\mathsf{rr}_{\mathsf{prep}}$ ,  $\mathsf{rr}_{\mathsf{exec}}$  and  $\mathsf{rr}_{\mathsf{postp}}$  are the reply registers of the execution handling operations  $O_{\mathsf{fetch}}$ ,  $O_{\mathsf{prep}}$ ,  $O_{\mathsf{exec}}$  and  $O_{\mathsf{postp}}$ , respectively. It is assumed that pcbr, pc, ir, ditr, bar, dr, eitr, irr, rr<sub>fetch</sub>, rr<sub>prep</sub>, rr<sub>exec</sub> and rr<sub>postp</sub> are pairwise different memory elements. Henceforth, we

write  $M'_{\rm ip}$  for {pcbr, pc, ir, ditr, bar, dr, eitr, irr} and  $M'_{\rm rr}$  for {rr<sub>fetch</sub>, rr<sub>prep</sub>, rr<sub>exec</sub>, rr<sub>postp</sub>}. It is assumed that  $M_{\rm prog} \cap (M'_{\rm ip} \cup M'_{\rm rr}) = \emptyset$ . Henceforth, we write  $\mathbb B$  for the set {T, F}. After giving the precise definition of an SP-NPL-enhancement, we will further explain how an SP-NPL-enhancement operates.

Let  $H = (M, B, \mathcal{S}, \mathcal{O}, A, \llbracket \_ \rrbracket)$  be a Maurer machine such that  $M \cap (\mathsf{M}_{\mathsf{prog}} \cup M'_{\mathsf{ip}} \cup M'_{\mathsf{rr}}) = \emptyset$  and fetch, prep, exec, postp  $\not\in A$ , and let  $(O_a, m_a) = \llbracket a \rrbracket$  for all  $a \in A$ . Then the  $\mathit{SP-NPL-enhancement}$  of H is the Maurer machine  $H' = (M', B', \mathcal{S}', \mathcal{O}', A', \llbracket \_ \rrbracket')$  such that

```

\begin{array}{ll} M' &= M \cup \mathsf{M}_{\mathsf{prog}} \cup M'_{\mathsf{ip}} \cup M'_{\mathsf{rr}} \;, \\ B' &= B \cup \mathsf{MA'}_{\mathsf{prog}} \cup \Im_{\mathsf{prog}} \cup IT \cup A \cup \mathbb{B} \;, \\ \mathcal{S}' &= \left\{S' : M' \to B' \mid \right. \\ & \left. S' \upharpoonright M \in \mathcal{S} \wedge S' \upharpoonright \mathsf{M}_{\mathsf{prog}} \in \mathsf{S}_{\mathsf{prog}} \wedge S'(\mathsf{pcbr}) \in \mathsf{MA}_{\mathsf{prog}} \wedge \right. \\ & \left. S'(\mathsf{pc}) \in \mathsf{MA'}_{\mathsf{prog}} \wedge S'(\mathsf{ir}) \in \Im_{\mathsf{prog}} \wedge \right. \\ & \left. S'(\mathsf{ditr}) \in IT \wedge S'(\mathsf{bar}) \in A \wedge S'(\mathsf{dr}) \in \mathsf{MA}_{\mathsf{prog}} \wedge \right. \\ & \left. S'(\mathsf{eitr}) \in IT \wedge S'(\mathsf{irr}) \in \mathbb{B} \wedge \right. \\ & \left. S'(\mathsf{rr}_{\mathsf{fetch}}) \in \mathbb{B} \wedge S'(\mathsf{rr}_{\mathsf{prep}}) \in \mathbb{B} \wedge S'(\mathsf{rr}_{\mathsf{exec}}) \in \mathbb{B} \wedge S'(\mathsf{rr}_{\mathsf{postp}}) \in \mathbb{B} \right\} \;, \\ & \left. S'(\mathsf{rr}_{\mathsf{fetch}}) \in \mathbb{B} \wedge S'(\mathsf{rr}_{\mathsf{prep}}) \in \mathbb{B} \wedge S'(\mathsf{rr}_{\mathsf{exec}}) \in \mathbb{B} \wedge S'(\mathsf{rr}_{\mathsf{postp}}) \in \mathbb{B} \right\} \;, \\ & \left. S' \in \mathcal{S}' \to \mathcal{S}' \mid \right. \\ & \left. S' \in \mathcal{S}' : \mathcal{S}' \in \mathcal{S}' : \mathcal{S}'

```

$O_{\mathsf{fetch}}$  is the unique function from  $\mathcal{S}'$  to  $\mathcal{S}'$  such that for all  $S' \in \mathcal{S}'$ :

```

O_{\mathsf{fetch}}(S') \upharpoonright M

=S' \upharpoonright M,

= S' \upharpoonright \mathsf{M}_{\mathsf{prog}},

O_{\mathsf{fetch}}(S') \upharpoonright \mathsf{M}_{\mathsf{prog}}

O_{\mathsf{fetch}}(S')(\mathsf{pcbr})

= S'(pcbr),

O_{\mathsf{fetch}}(S')(\mathsf{pc})

= S'(pc) + 1

if S'(pc) + 1 \leq S'(pcbr),

O_{\mathsf{fetch}}(S')(\mathsf{pc})

= S'(pc)

if S'(pc) + 1 > S'(pcbr),

=S'(\mathsf{M}_{\mathsf{prog}}[S'(\mathsf{pc})]) \ \text{ if } S'(\mathsf{pc}) \leq S'(\mathsf{pcbr}) \ ,

O_{\mathsf{fetch}}(S')(\mathsf{ir})

O_{\mathsf{fetch}}(S')(\mathsf{ir})

= #0

if S'(pc) > S'(pcbr),

O_{\mathsf{fetch}}(S') \upharpoonright \{\mathsf{ditr}, \mathsf{bar}, \mathsf{dr}\} = S' \upharpoonright \{\mathsf{ditr}, \mathsf{bar}, \mathsf{dr}\},

O_{\mathsf{fetch}}(S') \upharpoonright \{\mathsf{eitr}, \mathsf{irr}\}

=S' \upharpoonright \{ eitr, irr \},

O_{\mathsf{fetch}}(S')(\mathsf{rr}_{\mathsf{fetch}})

= T

if S'(pc) \leq S'(pcbr),

O_{\mathsf{fetch}}(S')(\mathsf{rr}_{\mathsf{fetch}})

= F

if S'(pc) > S'(pcbr),

O_{\mathsf{fetch}}(S') \upharpoonright (M'_{\mathsf{rr}} \setminus \{\mathsf{rr}_{\mathsf{fetch}}\}) = S' \upharpoonright (M'_{\mathsf{rr}} \setminus \{\mathsf{rr}_{\mathsf{fetch}}\}) \;.

```

14

$O_{\mathsf{prep}}$  is the unique function from  $\mathcal{S}'$  to  $\mathcal{S}'$  such that for all  $S' \in \mathcal{S}'$ :

```

=S' \upharpoonright M,

O_{\mathsf{prep}}(S') \upharpoonright M

=S' \upharpoonright \mathsf{M}_{\mathsf{prog}},

O_{\mathsf{prep}}(S') \upharpoonright \mathsf{M}_{\mathsf{prog}}

O_{\mathsf{prep}}(S')(\mathsf{pcbr})

= S'(pcbr),

O_{\mathsf{prep}}(S') \upharpoonright \{\mathsf{pc}, \mathsf{ir}\}

=S' \upharpoonright \{\mathsf{pc},\mathsf{ir}\}\ ,

O_{\mathsf{prep}}(S')(\mathsf{ditr})

= \mathfrak{p}_1(dec(S')),

O_{\mathsf{prep}}(S')(\mathsf{bar})

= \mathfrak{p}_2(dec(S')),

= \mathfrak{p}_3(dec(S')) ,

O_{\mathsf{prep}}(S')(\mathsf{dr})

O_{\mathsf{prep}}(S') \upharpoonright \{\mathsf{eitr}, \mathsf{irr}\}

=S' \upharpoonright \{ eitr, irr \},

O_{\mathsf{prep}}(S')(\mathsf{rr}_{\mathsf{prep}})

= T,

O_{\mathsf{prep}}(S') \upharpoonright (M'_{\mathsf{rr}} \setminus \{\mathsf{rr}_{\mathsf{prep}}\}) = S' \upharpoonright (M'_{\mathsf{rr}} \setminus \{\mathsf{rr}_{\mathsf{prep}}\}) \;,

```

where  $dec: \mathcal{S}' \to IT \times A \times \mathsf{MA}_{\mathsf{prog}}$  is defined as follows:

```

\begin{split} & dec(S') = (\mathsf{bsc}, a, S'(\mathsf{dr})) & \text{if } S'(\mathsf{ir}) = a \;, \\ & dec(S') = (\mathsf{ptst}, a, S'(\mathsf{dr})) & \text{if } S'(\mathsf{ir}) = +a \;, \\ & dec(S') = (\mathsf{ntst}, a, S'(\mathsf{dr})) & \text{if } S'(\mathsf{ir}) = -a \;, \\ & dec(S') = (\mathsf{fjmp}, S'(\mathsf{bar}), k) & \text{if } S'(\mathsf{ir}) = \#k \;, \\ & dec(S') = (\mathsf{term}, S'(\mathsf{bar}), S'(\mathsf{dr})) & \text{if } S'(\mathsf{ir}) = ! \;. \end{split}

```

$O_{\mathsf{exec}}$  is the unique function from  $\mathcal{S}'$  to  $\mathcal{S}'$  such that for all  $S' \in \mathcal{S}'$ :

```

O_{\mathsf{exec}}(S') \upharpoonright M

= O_{S'(\mathsf{bar})}(S' \upharpoonright M)

if opc(S'),

=S' \upharpoonright M

O_{\mathsf{exec}}(S') \upharpoonright M

if \neg opc(S'),

= S' \upharpoonright \mathsf{M}_{\mathsf{prog}},

O_{\mathsf{exec}}(S') \upharpoonright \mathsf{M}_{\mathsf{prog}}

= S'(pcbr),

O_{\mathsf{exec}}(S')(\mathsf{pcbr})

=S' \upharpoonright \{\mathsf{pc},\mathsf{ir}\}\ ,

O_{\mathsf{exec}}(S') \upharpoonright \{\mathsf{pc}, \mathsf{ir}\}

O_{\mathsf{exec}}(S') \upharpoonright \{\mathsf{ditr}, \mathsf{bar}, \mathsf{dr}\}

=S' \upharpoonright \{\mathsf{ditr},\mathsf{bar},\mathsf{dr}\}\ ,

O_{\mathsf{exec}}(S')(\mathsf{eitr})

= S'(ditr),

=O_{S'(\mathsf{bar})}(S' \upharpoonright M)(m_{S'(\mathsf{bar})}) \text{ if } opc(S'),

O_{\mathsf{exec}}(S')(\mathsf{irr})

if \neg opc(S'),

O_{\mathsf{exec}}(S')(\mathsf{irr})

= T

O_{\mathsf{exec}}(S')(\mathsf{rr}_{\mathsf{exec}})

= T,

O_{\mathsf{exec}}(S') \upharpoonright (M'_{\mathsf{rr}} \setminus \{\mathsf{rr}_{\mathsf{exec}}\}) = S' \upharpoonright (M'_{\mathsf{rr}} \setminus \{\mathsf{rr}_{\mathsf{exec}}\}) \;,

```

where  $opc: \mathcal{S}' \to \mathbb{B}$  is defined as follows:

$$opc(S') = T \text{ iff } S'(\mathsf{ditr}) \in \{\mathsf{bsc}, \mathsf{ptst}, \mathsf{ntst}\}\ .$$

$O_{\mathsf{postp}}$  is the unique function from  $\mathcal{S}'$  to  $\mathcal{S}'$  such that for all  $S' \in \mathcal{S}'$ :

```

=S' \upharpoonright M,

O_{\mathsf{postp}}(S') \upharpoonright M

O_{\mathsf{postp}}(S') \upharpoonright \mathsf{M}_{\mathsf{prog}}

= S' \upharpoonright \mathsf{M}_{\mathsf{prog}},

O_{\mathsf{postp}}(S')(\mathsf{pcbr})

= S'(pcbr),

= pcu(S'),

O_{\mathsf{postp}}(S')(\mathsf{pc})

O_{\mathsf{postp}}(S')(\mathsf{ir})

= S'(ir),

O_{\mathsf{postp}}(S') \upharpoonright \{\mathsf{ditr}, \mathsf{bar}, \mathsf{dr}\} = S' \upharpoonright \{\mathsf{ditr}, \mathsf{bar}, \mathsf{dr}\},

O_{\mathsf{postp}}(S') \upharpoonright \{\mathsf{eitr}, \mathsf{irr}\}

=S' \upharpoonright \{\mathsf{eitr},\mathsf{irr}\}\;,

O_{\mathsf{postp}}(S')(\mathsf{rr}_{\mathsf{postp}})

if S'(eitr) \neq term,

if S'(eitr) = term,

O_{\mathsf{postp}}(S')(\mathsf{rr}_{\mathsf{postp}})

O_{\mathsf{postp}}(S') \upharpoonright (M'_{\mathsf{rr}} \setminus \{\mathsf{rr}_{\mathsf{postp}}\}) = S' \upharpoonright (M'_{\mathsf{rr}} \setminus \{\mathsf{rr}_{\mathsf{postp}}\}) \;,

```

where  $pcu: \mathcal{S}' \to \mathsf{MA'_{prog}}$  is defined as follows:

```

pcu(S') = S'(pc)

if S'(\mathsf{eitr}) = \mathsf{bsc} \vee

S'(\mathsf{eitr}) = \mathsf{ptst} \land S'(\mathsf{irr}) = \mathsf{T} \lor

S'(\mathsf{eitr}) = \mathsf{ntst} \land S'(\mathsf{irr}) = \mathsf{F} \lor

S'(eitr) = term,

if (S'(\mathsf{eitr}) = \mathsf{ptst} \land S'(\mathsf{irr}) = \mathsf{F} \lor

pcu(S') = S'(pc) + 1

S'(\mathsf{eitr}) = \mathsf{ntst} \land S'(\mathsf{irr}) = \mathsf{T}) \land

S'(pc) + 1 \le S'(pcbr),

pcu(S') = S'(pc) - 1 + S'(dr) if S'(eitr) = fjmp \land S'(dr) \neq 0 \land

S'(pc) - 1 + S'(dr) \le S'(pcbr)

pcu(S') = S'(pcbr) + 1

if (S'(\mathsf{eitr}) = \mathsf{ptst} \land S'(\mathsf{irr}) = \mathsf{F} \lor

S'(\mathsf{eitr}) = \mathsf{ntst} \land S'(\mathsf{irr}) = \mathsf{T}) \land

S'(pc) + 1 > S'(pcbr) \vee

S'(\mathsf{eitr}) = \mathsf{fimp} \land

(S'(\mathsf{dr}) = 0 \vee

S'(pc) - 1 + S'(dr) > S'(pcbr).

```

Figure 1 shows the structure of an SP-NPL-enhancement. The program counter pc contains the address of the program memory element from which a PGA instruction is fetched next, unless its content is greater than the highest program address (contained in pcbr). Fetched PGA instructions are stored in ir. The program counter is incremented at every fetch. Pre-processing amounts to decoding the PGA instruction stored in ir: the type of that PGA instruction is stored in ditr, the basic action involved is stored in bar if it is not a jump or termination instruction, and the displacement is stored in dr if it is a jump instruction. Execution does not deal with jump and termination instructions; they are dealt with by post-processing. Post-processing amounts to adjusting the program counter and recognizing termination. The program counter is adjusted on a positive test instruction that has given a negative reply, a negative test instruction that has given a positive reply, and a jump instruction.

Essential information about the last fetched PGA instruction is forwarded from one execution handling operation to the next: from  $O_{\text{fetch}}$  to  $O_{\text{prep}}$  via ir, from  $O_{\text{prep}}$  to  $O_{\text{exec}}$  via ditr and either bar or dr, from  $O_{\text{exec}}$  to  $O_{\text{postp}}$  via eitr and irr. Moreover, each execution

Fig. 1. Structure of an SP-NPL-enhancement

handling operation has its own reply register. All this fits in well with the pipelined variant of SP-NPL-enhancements that will be introduced in Section 8.

Because the memory is extended with only finitely many memory elements, it is easy to check, using Proposition IV in Maurer (1966), that the SP-NPL-enhancement of a Maurer machine is indeed a Maurer machine. The same remark applies to the SP-PL-enhancement of a Maurer machine introduced in Section 8 as well.

Consider the guarded recursive specification over BTA that consists of the following equation:

$$CT = (\mathsf{prep} \circ \mathsf{exec} \circ (CT \lhd \mathsf{postp} \rhd \mathsf{S})) \lhd \mathsf{fetch} \rhd \mathsf{D}$$

.

Let P be a finite PGA program. Then applying thread |P| to a state of Maurer machine H has the same effect as applying the execution handling thread CT to the corresponding state of the SP-NPL-enhancement of H in which the program memory contains the stored representation of P. This is stated rigorously in the following theorem.

Theorem 1 (SP-NPL-enhancement). Let  $H' = (M', B', \mathcal{S}', \mathcal{O}', A', \llbracket \_ \rrbracket')$  be the SP-NPL-enhancement of  $H = (M, B, \mathcal{S}, \mathcal{O}, A, \llbracket \_ \rrbracket)$ , let  $P = u_1 ; \ldots ; u_n \in \mathcal{P}_{\mathsf{fin}}(A)$  be such that  $n \leq \mathit{size}(\mathsf{M}_{\mathsf{prog}})$ , and let  $S'_0 \in \mathcal{S}'$  be such that  $S'_0 \upharpoonright \mathsf{M}_{\mathsf{prog}}[0, n-1] = \mathsf{s}_{\mathsf{prog}}(P)$ ,  $S'_0(\mathsf{pcbr}) = n-1$  and  $S'_0(\mathsf{pc}) = 0$ . Then  $|P| \bullet_H (S'_0 \upharpoonright M) = (CT \bullet_{H'} S'_0) \upharpoonright M$ .

*Proof.* Let  $(O_a, m_a) = \llbracket a \rrbracket$  for all  $a \in A$ , and let  $(O_a, \mathsf{rr}_a) = \llbracket a \rrbracket'$  for all  $a \in A'$ . Then it is easy to see that for all  $S' \in \mathcal{S}'$  and  $a \in A$  such that  $S'(\mathsf{pc}) \leq S'(\mathsf{pcbr})$  and  $S'(\mathsf{M}_{\mathsf{prog}}[S'(\mathsf{pc})]) \in \{a, +a, -a\}$ :

$$O_{\mathsf{postp}}(O_{\mathsf{exec}}(O_{\mathsf{prep}}(O_{\mathsf{fetch}}(S')))) \upharpoonright M = O_a(S' \upharpoonright M) , \tag{1}$$

$$O_{\mathsf{postp}}(O_{\mathsf{exec}}(O_{\mathsf{prep}}(O_{\mathsf{fetch}}(S'))))(\mathsf{irr}) \quad = \quad O_a(S' \upharpoonright M)(m_a) \; ; \tag{2}$$

and it is easy to see that for all  $S' \in \mathcal{S}'$  and  $a \in A$  such that  $S'(\mathsf{pc}) \leq S'(\mathsf{pcbr})$  and  $S'(\mathsf{M}_{\mathsf{prog}}[S'(\mathsf{pc})]) \notin \{a, +a, -a\}$ :

$$O_{\mathsf{postp}}(O_{\mathsf{exec}}(O_{\mathsf{prep}}(O_{\mathsf{fetch}}(S')))) \upharpoonright M = S' \upharpoonright M . \tag{3}$$

Let  $(p'_i, S'_i)$  be the (i+1)st element in the full path of  $(CT, S'_0)$  on H'. Then it is easy to prove by induction on i that

$$\begin{array}{ll} p'_{4i+4} = CT & \text{if } S'_{4i+1}(\mathsf{rr}_{\mathsf{fetch}}) = \mathsf{T} \wedge S'_{4i+4}(\mathsf{rr}_{\mathsf{postp}}) = \mathsf{T} \;, \\ p'_{4i+4} = \mathsf{S} & \text{if } S'_{4i+1}(\mathsf{rr}_{\mathsf{fetch}}) = \mathsf{T} \wedge S'_{4i+4}(\mathsf{rr}_{\mathsf{postp}}) = \mathsf{F} \;, \\ p'_{4i+1} = \mathsf{D} & \text{if } S'_{4i+1}(\mathsf{rr}_{\mathsf{fetch}}) = \mathsf{F} \end{array} \tag{4}$$

(if  $4i+4 < \|(CT,S_0')\|_{H'}$  in case CT converges from  $S_0'$  on H'). Let  $(p_i,S_i)$  be the (i+1)st element in the full path of  $(|P|,S_0' \upharpoonright M)$  on H, and let  $(p_i',S_i')$  be the (i+1)st element in the full path of  $(CT,S_0')$  on H' of which the first component equals CT, S or D and the second component, say S', satisfies  $S'(\mathsf{M}_{\mathsf{prog}}[S'(\mathsf{pc})]) \neq \#k$  for all  $k \in \mathsf{MA}_{\mathsf{prog}}$ . Then, using (1), (2), (3) and (4), it is straightforward to prove by induction on i and case distinction on the structure of finite PGA programs that

$$\begin{aligned} p_i &= |\mathsf{s}_{\mathsf{prog}}(P)(\mathsf{M}_{\mathsf{prog}}[S'_{4i}(\mathsf{pc})]) \; ; \ldots \; ; \mathsf{s}_{\mathsf{prog}}(P)(\mathsf{M}_{\mathsf{prog}}[n-1])| \; , \\ S_i &= S'_{4i} \upharpoonright M \end{aligned}$$

(if  $i < \|(|P|, S'_0 \upharpoonright M)\|_H$  in case |P| converges from  $S'_0 \upharpoonright M$  on H). From this, the theorem follows immediately.

Henceforth, execution handling threads, like CT, are called *power threads*.

## 8. Pipelined Instruction Processing

In this section, we model a micro-architecture with pipelined instruction processing which is a variant of the micro-architecture with non-pipelined instruction processing modelled in Section 7. In the latter micro-architecture, PGA instructions are processed after one another, whereas, in the micro-architecture modelled here, four PGA instructions can be simultaneously overlapped in processing. We again start from an arbitrary Maurer machine and enhance it.

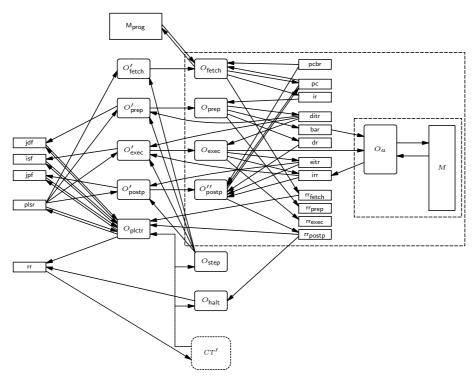

We enhance Maurer machines by extending the memory as in the case of SP-NPL-enhancements and additionally with an instruction skip flag (isf), a jump decoded flag (jdf), a jump processed flag (jpf), a pipeline status register (plsr) and a reply register (rr), and the operation set with a step operation  $(O_{\text{step}})$ , a pipeline control operation  $(O_{\text{plctr}})$  and a halt operation  $(O_{\text{halt}})$ . Moreover, we replace the basic actions of the original Maurer machine by basic actions step, plctr and halt with which the extra operations  $O_{\text{step}}$ ,  $O_{\text{plctr}}$  and  $O_{\text{halt}}$  are associated. The resulting Maurer machines are called SP-PL-enhancements. SP again stands for stored program and PL stands for pipelined instruction processing. In SP-PL-enhancements of Maurer machines, the four pipeline stages fetchst, prepst, execst and postpst are distinguished. Henceforth, we write PS for {fetchst, prepst, execst, postpst}. The memory elements isf, jdf, jpf and plsr are used to control the pipelined processing of PGA instructions and to produce a reply in rr at the completion of each step of the pipelined instruction processing. It is assumed that isf, jdf, jpf, plsr and rr are pairwise different memory elements. Henceforth, we write  $M'_{\text{plc}}$  for {isf, jdf, jpf, plsr, rr}. It is assumed that  $(M_{\text{prog}} \cup M'_{\text{ip}} \cup M'_{\text{rr}}) \cap M'_{\text{plc}} = \emptyset$ . After

giving the precise definition of an SP-PL-enhancement, we will further explain how an SP-PL-enhancement operates.

Let  $H = (M, B, \mathcal{S}, \mathcal{O}, A, \llbracket - \rrbracket)$  be a Maurer machine such that  $M \cap (\mathsf{M}_{\mathsf{prog}} \cup M'_{\mathsf{ip}} \cup M'_{\mathsf{rr}} \cup M'_{\mathsf{plc}}) = \emptyset$  and step, plctr, halt  $\notin A$ , and let  $(O_a, m_a) = \llbracket a \rrbracket$  for all  $a \in A$ . Then the SP-PL-enhancement of H is the Maurer machine  $H' = (M', B', \mathcal{S}', \mathcal{O}', A', \llbracket - \rrbracket')$  such that

```

\begin{array}{ll} M' &= M \cup \mathsf{M}_{\mathsf{prog}} \cup M'_{\mathsf{ip}} \cup M'_{\mathsf{rr}} \cup M'_{\mathsf{plc}} \;, \\ B' &= B \cup \mathsf{MA}'_{\mathsf{prog}} \cup \mathfrak{I}_{\mathsf{prog}} \cup IT \cup A \cup \mathbb{B} \cup \mathcal{P}(PS) \;, \\ \mathcal{S}' &= \left\{S' : M' \to B' \mid \\ & S' \upharpoonright M \in \mathcal{S} \wedge S' \upharpoonright \mathsf{M}_{\mathsf{prog}} \in \mathsf{S}_{\mathsf{prog}} \wedge S'(\mathsf{pcbr}) \in \mathsf{MA}_{\mathsf{prog}} \wedge \\ & S'(\mathsf{pc}) \in \mathsf{MA}'_{\mathsf{prog}} \wedge S'(\mathsf{ir}) \in \mathfrak{I}_{\mathsf{prog}} \wedge \\ & S'(\mathsf{ditr}) \in IT \wedge S'(\mathsf{bar}) \in A \wedge S'(\mathsf{dr}) \in \mathsf{MA}_{\mathsf{prog}} \wedge \\ & S'(\mathsf{eitr}) \in IT \wedge S'(\mathsf{irr}) \in \mathbb{B} \wedge \\ & S'(\mathsf{rrf}_{\mathsf{etch}}) \in \mathbb{B} \wedge S'(\mathsf{rrpep}) \in \mathbb{B} \wedge S'(\mathsf{rrexec}) \in \mathbb{B} \wedge S'(\mathsf{rrpostp}) \in \mathbb{B} \wedge \\ & S'(\mathsf{jdf}) \in \mathbb{B} \wedge S'(\mathsf{isf}) \in \mathbb{B} \wedge S'(\mathsf{jpf}) \in \mathbb{B} \wedge S'(\mathsf{plsr}) \in \mathcal{P}(PS) \wedge \\ & S'(\mathsf{rr}) \in \mathbb{B} \} \;, \\ \mathcal{O}' &= \left\{O' : \mathcal{S}' \to \mathcal{S}' \mid \\ & \exists O \in \mathcal{O} \bullet \forall S' \in \mathcal{S}' \bullet \\ & (O'(S') \upharpoonright M = O(S' \upharpoonright M) \wedge O'(S') \upharpoonright (M' \setminus M) = S' \upharpoonright (M' \setminus M)) \right\} \\ & \cup \left\{O_{\mathsf{step}}, O_{\mathsf{plctr}}, O_{\mathsf{halt}} \right\} \;, \\ \mathcal{A}' &= \left\{\mathsf{step}, \mathsf{plctr}, \mathsf{halt} \right\} \;, \\ \llbracket a \rrbracket' &= (O_a, \mathsf{rr}) \quad \text{for all } a \in A' \;. \end{array}

```

$O_{\mathsf{step}}$  is the unique function from  $\mathcal{S}'$  to  $\mathcal{S}'$  such that for all  $S' \in \mathcal{S}'$ :

$$O_{\mathsf{step}}(S') = O'_{\mathsf{fetch}}(O'_{\mathsf{prep}}(O'_{\mathsf{exec}}(O'_{\mathsf{postp}}(S')))) \;,$$

where  $O'_{\text{fetch}}$ ,  $O'_{\text{prep}}$ ,  $O'_{\text{exec}}$  and  $O'_{\text{postp}}$  are suboperations defined as follows:

$O'_{\mathsf{fetch}}$  is the unique function from  $\mathcal{S}'$  to  $\mathcal{S}'$  such that for all  $S' \in \mathcal{S}'$ :

$$\begin{array}{ll} O'_{\mathsf{fetch}}(S') &= S' & \text{if fetchst } \not \in S'(\mathsf{plsr}) \; , \\ O'_{\mathsf{fetch}}(S') \upharpoonright (M' \setminus M'_{\mathsf{plc}}) &= O_{\mathsf{fetch}}(S' \upharpoonright (M' \setminus M'_{\mathsf{plc}})) & \text{if fetchst } \in S'(\mathsf{plsr}) \; , \\ O'_{\mathsf{fetch}}(S') \upharpoonright M'_{\mathsf{plc}} &= S' \upharpoonright M'_{\mathsf{plc}} & \text{if fetchst } \in S'(\mathsf{plsr}) \; ; \end{array}$$

$O'_{\mathsf{prep}}$  is the unique function from  $\mathcal{S}'$  to  $\mathcal{S}'$  such that for all  $S' \in \mathcal{S}'$ :

```

\begin{array}{lll} O'_{\mathsf{prep}}(S') & = S' & \text{if prepst } \not\in S'(\mathsf{plsr}) \;, \\ O'_{\mathsf{prep}}(S') \upharpoonright (M' \setminus M'_{\mathsf{plc}}) & = O_{\mathsf{prep}}(S' \upharpoonright (M' \setminus M'_{\mathsf{plc}})) & \text{if prepst } \in S'(\mathsf{plsr}) \;, \\ O'_{\mathsf{prep}}(S')(\mathsf{jdf}) & = jdc(S') & \text{if prepst } \in S'(\mathsf{plsr}) \;, \\ O'_{\mathsf{prep}}(S') \upharpoonright (M'_{\mathsf{plc}} \setminus \{\mathsf{jdf}\}) & \text{if prepst } \in S'(\mathsf{plsr}) \;, \end{array}

```

where  $jdc: \mathcal{S}' \to \mathbb{B}$  is the unique function from  $\mathcal{S}'$  to  $\mathbb{B}$  such that for all  $S' \in \mathcal{S}'$ :

$$jdc(S') = \mathsf{T} \; \mathsf{iff} \; O_{\mathsf{prep}}(S' \upharpoonright (M' \setminus M'_{\mathsf{plc}}))(\mathsf{ditr}) \in \{\mathsf{fjmp}, \mathsf{term}\} \; ;$$

$O'_{\mathsf{exec}}$  is the unique function from  $\mathcal{S}'$  to  $\mathcal{S}'$  such that for all  $S' \in \mathcal{S}'$ :

```

\begin{array}{ll} O_{\mathsf{exec}}'(S') &= S' & \text{if execst } \not\in S'(\mathsf{plsr}) \;, \\ O_{\mathsf{exec}}'(S') \upharpoonright (M' \setminus M'_{\mathsf{plc}}) &= O_{\mathsf{exec}}(S' \upharpoonright (M' \setminus M'_{\mathsf{plc}})) \; \text{if execst} \in S'(\mathsf{plsr}) \;, \\ O_{\mathsf{exec}}'(S')(\mathsf{isf}) &= isc(S') & \text{if execst} \in S'(\mathsf{plsr}) \;, \\ O_{\mathsf{exec}}'(S') \upharpoonright (M'_{\mathsf{plc}} \setminus \{\mathsf{isf}\}) &= S' \upharpoonright (M'_{\mathsf{plc}} \setminus \{\mathsf{isf}\}) & \text{if execst} \in S'(\mathsf{plsr}) \;, \end{array}

```

where  $isc: \mathcal{S}' \to \mathbb{B}$  is the unique function from  $\mathcal{S}'$  to  $\mathbb{B}$  such that for all  $S' \in \mathcal{S}'$ :

$$\begin{split} isc(S') &= \mathsf{T} \text{ iff } \\ S'(\mathsf{ditr}) &= \mathsf{ptst} \wedge O_{\mathsf{exec}}(S' \upharpoonright (M' \setminus M'_{\mathsf{plc}}))(\mathsf{irr}) = \mathsf{F} \vee \\ S'(\mathsf{ditr}) &= \mathsf{ntst} \wedge O_{\mathsf{exec}}(S' \upharpoonright (M' \setminus M'_{\mathsf{plc}}))(\mathsf{irr}) = \mathsf{T} \ ; \end{split}$$

$O'_{\mathsf{postp}}$  is the unique function from  $\mathcal{S}'$  to  $\mathcal{S}'$  such that for all  $S' \in \mathcal{S}'$ :

$$\begin{array}{ll} O_{\mathsf{postp}}'(S') &= S' & \text{if postpst} \not\in S'(\mathsf{plsr}) \;, \\ O_{\mathsf{postp}}'(S') \upharpoonright (M' \setminus M_{\mathsf{plc}}') &= O_{\mathsf{postp}}''(S' \upharpoonright (M' \setminus M_{\mathsf{plc}}')) \; \text{if postpst} \in S'(\mathsf{plsr}) \;, \\ O_{\mathsf{postp}}'(S')(\mathsf{jpf}) &= \mathit{jpc}(S') & \text{if postpst} \in S'(\mathsf{plsr}) \;, \\ O_{\mathsf{postp}}'(S') \upharpoonright (M_{\mathsf{plc}}' \setminus \{\mathsf{jpf}\}) &= S' \upharpoonright (M_{\mathsf{plc}}' \setminus \{\mathsf{jpf}\}) & \text{if postpst} \in S'(\mathsf{plsr}) \;, \end{array}$$

where  $jpc: \mathcal{S}' \to \mathbb{B}$  is the unique function from  $\mathcal{S}'$  to  $\mathbb{B}$  such that for all  $S' \in \mathcal{S}'$ :

$$jpc(S') = T \text{ iff } S'(\text{eitr}) = \text{fjmp },$$

and  $O''_{\mathsf{postp}}$  is defined as  $O_{\mathsf{postp}}$  in the case of the SP-NPL-enhancement, except for the replacement of the auxiliary program counter update function pcu by the function pcu' defined as follows:

$$\begin{split} pcu'(S') &= S'(\mathsf{pc}) & \text{if } S'(\mathsf{eitr}) \neq \mathsf{fjmp} \;, \\ pcu'(S') &= S'(\mathsf{pc}) - 2 + S'(\mathsf{dr}) \; \text{if } S'(\mathsf{eitr}) = \mathsf{fjmp} \land S'(\mathsf{dr}) \neq 0 \land \\ & S'(\mathsf{pc}) - 2 + S'(\mathsf{dr}) \leq S'(\mathsf{pcbr}) \;, \\ pcu'(S') &= S'(\mathsf{pcbr}) + 1 & \text{if } S'(\mathsf{eitr}) = \mathsf{fjmp} \land \\ & (S'(\mathsf{dr}) = 0 \lor \\ & S'(\mathsf{pc}) - 2 + S'(\mathsf{dr}) > S'(\mathsf{pcbr})) \;. \end{split}$$

$O_{\mathsf{plctr}}$  is the unique function from  $\mathcal{S}'$  to  $\mathcal{S}'$  such that for all  $S' \in \mathcal{S}'$ :

$$\begin{split} O_{\mathsf{plctr}}(S') \upharpoonright (M' \setminus M'_{\mathsf{plc}}) &= S' \upharpoonright (M' \setminus M'_{\mathsf{plc}}) \;, \\ O_{\mathsf{plctr}}(S')(\mathsf{jdf}) &= \mathsf{F} \;, \\ O_{\mathsf{plctr}}(S')(\mathsf{isf}) &= \mathsf{F} \;, \\ O_{\mathsf{plctr}}(S')(\mathsf{jpf}) &= \mathsf{F} \;, \\ O_{\mathsf{plctr}}(S')(\mathsf{plsr}) &= plsu(S') \;, \\ O_{\mathsf{plctr}}(S')(\mathsf{rr}) &= ru(S') \;, \end{split}$$

where  $plsu: \mathcal{S}' \to \mathcal{P}(PS)$  is the unique function from  $\mathcal{S}'$  to  $\mathcal{P}(PS)$  such that for all

Fig. 2. Structure of an SP-PL-enhancement

$S' \in \mathcal{S}'$ :

$$\begin{split} \mathsf{fetchst} \in \mathit{plsu}(S') & \text{ iff } S'(\mathsf{rr}_\mathsf{fetch}) = \mathsf{T} \land \\ & (\mathsf{fetchst} \in S'(\mathsf{plsr}) \land S'(\mathsf{jdf}) = \mathsf{F} \lor \\ & S'(\mathsf{isf}) = \mathsf{T} \lor S'(\mathsf{jpf}) = \mathsf{T}) \ , \\ \mathsf{prepst} \in \mathit{plsu}(S') & \text{ iff } S'(\mathsf{rr}_\mathsf{fetch}) = \mathsf{T} \land \\ & (\mathsf{fetchst} \in S'(\mathsf{plsr}) \land S'(\mathsf{jdf}) = \mathsf{F} \lor \\ & S'(\mathsf{isf}) = \mathsf{T}) \ , \\ \mathsf{execst} \in \mathit{plsu}(S') & \text{ iff } \mathsf{prepst} \in S'(\mathsf{plsr}) \land S'(\mathsf{isf}) = \mathsf{F} \ , \\ \mathsf{postpst} \in \mathit{plsu}(S') & \text{ iff } \mathsf{execst} \in S'(\mathsf{plsr}) \ , \\ \end{split}$$

and  $ru: \mathcal{S}' \to \mathbb{B}$  is the unique function from  $\mathcal{S}'$  to  $\mathbb{B}$  such that for all  $S' \in \mathcal{S}'$ :

$$ru(S') = \mathsf{T} \ \ \text{iff} \ \ plsu(S') \neq \emptyset \wedge S'(\mathsf{rr}_{\mathsf{postp}}) = \mathsf{T} \ .$$

$O_{\mathsf{halt}}$  is the unique function from  $\mathcal{S}'$  to  $\mathcal{S}'$  such that for all  $S' \in \mathcal{S}'$ :

$$\begin{array}{ll} O_{\mathsf{halt}}(S') \upharpoonright (M' \setminus \{\mathsf{rr}\}) = S' \upharpoonright (M' \setminus \{\mathsf{rr}\}) \;, \\ O_{\mathsf{halt}}(S')(\mathsf{rr}) &= \mathsf{T} & \mathsf{if} \; S'(\mathsf{rr}_{\mathsf{postp}}) = \mathsf{F} \;, \\ O_{\mathsf{halt}}(S')(\mathsf{rr}) &= \mathsf{F} & \mathsf{if} \; S'(\mathsf{rr}_{\mathsf{postp}}) = \mathsf{T} \;. \end{array}$$

Figure 2 shows the structure of an SP-PL-enhancement. The suboperations  $O'_{\mathsf{fetch}}$ ,  $O'_{\mathsf{prep}}$  and  $O'_{\mathsf{exec}}$  of  $O_{\mathsf{step}}$  either do not affect the memory elements of  $M' \setminus M'_{\mathsf{plc}}$  or do affect these memory elements exactly in the way in which the operations  $O_{\mathsf{fetch}}$ ,  $O_{\mathsf{prep}}$

and  $O_{\sf exec}$  of the SP-NPL-enhancement of H would affect them. The suboperation  $O'_{\sf postp}$  of  $O_{\sf step}$  either does not affect the memory elements of  $M' \setminus M'_{\sf plc}$  or does affect these memory elements in a way that is similar to the way in which the operation  $O_{\sf postp}$  of the SP-NPL-enhancement of H would affect them. The difference with  $O_{\sf postp}$  is due to the different way in which skipping of a PGA instruction is accomplished in pipelined instruction processing.

The suboperations  $O'_{\mathsf{fetch}}$ ,  $O'_{\mathsf{prep}}$ ,  $O'_{\mathsf{exec}}$  and  $O'_{\mathsf{postp}}$  of  $O_{\mathsf{step}}$  correspond to the pipeline stages that a PGA instruction being processed passes through successively. When the suboperation corresponding to a stage other than the last one has handled a PGA instruction, the suboperation corresponding to the next stage is enabled to handle that PGA instruction in the next step, subject to the exceptions mentioned below.  $O'_{\mathsf{fetch}}$ , the suboperation corresponding to the first stage, is always enabled to fetch a PGA instruction in the next step, subject to the exceptions mentioned below. The exceptions are the following:

- when  $O'_{prep}$  has decoded a jump or termination instruction, pipelined instruction processing is stalled beginning with the PGA instruction fetched in the same step;

- when  $O'_{\text{exec}}$  has executed either a positive test instruction with a negative reply as result or a negative test instruction with a positive reply as result, the PGA instruction fetched immediately after the test instruction is further discarded and pipelined instruction processing is started again with the next step if the latter instruction is a jump or termination instruction;

- when O'<sub>postp</sub> has adjusted the program counter on a jump instruction, the last fetched PGA instruction is discarded and pipelined instruction processing is started again with the next step.

Thus, the suboperations  $O'_{\mathsf{fetch}}$ ,  $O'_{\mathsf{prep}}$ ,  $O'_{\mathsf{exec}}$  and  $O'_{\mathsf{postp}}$  are not all enabled to handle a PGA instruction in every step of the pipelined instruction processing. The content of the pipeline status register indicates which of the suboperations are enabled. Enabledness is controlled by the pipeline control operation  $O_{\mathsf{plctr}}$ . This operation is intended to be performed immediately after  $O_{\mathsf{step}}$ . It takes parts of the output of the suboperations of  $O_{\mathsf{step}}$  to fix up the enabledness of these suboperations for the next step.

The idea is that in each step the suboperations  $O'_{\text{fetch}}$ ,  $O'_{\text{prep}}$ ,  $O'_{\text{exec}}$  and  $O'_{\text{postp}}$  are performed in parallel. To justify the use of the term pipeline here, we have to show that the suboperations can actually be performed in parallel. We come back to this issue in Section 9

Consider the guarded recursive specification over BTA that consists of the following equation:

$$CT' = \mathsf{step} \circ (CT' \unlhd \mathsf{plctr} \trianglerighteq (\mathsf{S} \unlhd \mathsf{halt} \trianglerighteq \mathsf{D}))$$

.

Let P be a finite PGA program. Then applying thread |P| to a state of the Maurer machine H has the same effect as applying power thread CT' to the corresponding state of the SP-PL-enhancement of H in which the program memory contains the stored representation of P. This is stated rigorously in the following theorem.

**Theorem 2 (SP-PL-enhancement).** Let  $H' = (M', B', \mathcal{S}', \mathcal{O}', A', [\![.]\!]')$  be the SP-

PL-enhancement of  $H = (M, B, \mathcal{S}, \mathcal{O}, A, \llbracket \_ \rrbracket)$ , let  $P = u_1 ; \ldots ; u_n \in \mathcal{P}_{\mathsf{fin}}(A)$  be such that  $n \leq \mathit{size}(\mathsf{M}_{\mathsf{prog}})$ , let  $S'_0 \in \mathcal{S}'$  be such that  $S'_0 \upharpoonright \mathsf{M}_{\mathsf{prog}}[0, n-1] = \mathsf{s}_{\mathsf{prog}}(P), S'_0(\mathsf{pcbr}) = n-1, S'_0(\mathsf{pc}) = 0, S'_0(\mathsf{rr}_{\mathsf{fetch}}) = \mathsf{T}, S'_0(\mathsf{jdf}) = S'_0(\mathsf{isf}) = S'_0(\mathsf{jpf}) = \mathsf{F} \text{ and } S'_0(\mathsf{plsr}) = \{\mathsf{fetchst}\}.$  Then  $|P| \bullet_H (S'_0 \upharpoonright M) = (CT' \bullet_{H'} S'_0) \upharpoonright M$ .

*Proof.* We prove that  $(CT \bullet_{H''} (S'_0 \upharpoonright (M' \setminus M'_{\operatorname{plc}}))) \upharpoonright M = (CT' \bullet_{H'} S'_0) \upharpoonright M$ , where H'' is the SP-NPL-enhancement of H. From this and Theorem 1, the theorem follows immediately.

We use the following notation in the proof. For each  $S' \in \mathcal{S}'$  and each n > 0,  $cycle^n(S')$  is defined by induction on n as follows:  $cycle^1(S') = O_{\mathsf{plctr}}(O_{\mathsf{step}}(S'))$  and  $cycle^{n+1}(S') = O_{\mathsf{plctr}}(O_{\mathsf{step}}(cycle^n(S')))$ . For each  $S' \in \mathcal{S}'$ , tip(S') is defined as follows:  $tip(S') \Leftrightarrow \mathsf{fetchst} \in S'(\mathsf{plsr}) \land \mathsf{prepst} \in cycle^1(S')(\mathsf{plsr}) \land \mathsf{execst} \in cycle^2(S')(\mathsf{plsr}) \land \mathsf{prepst} \in cycle^3(S')(\mathsf{plsr})$ . Thus, tip(S') indicates that some instruction will be totally processed from state S'.

Analysis of input and output regions yields three potential sources of interference between the suboperations of  $O_{\text{step}}$ :  $OR(O'_{\text{postp}}) \cap OR(O'_{\text{fetch}}) = \{\text{pc}\}$ ,  $OR(O'_{\text{postp}}) \cap IR(O'_{\text{fetch}}) = \{\text{pc}\}$  and  $IR(O'_{\text{postp}}) \cap OR(O'_{\text{fetch}}) = \{\text{pc}\}$ . It is easy to see that, by stalling pipelined instruction processing when  $O'_{\text{prep}}$  has decoded a jump instruction, interference does not really happen:  $O'_{\text{fetch}}$  does not change any memory element if  $O'_{\text{postp}}$  has changed pc in the same step, and  $O'_{\text{postp}}$  does not change any memory element if  $O'_{\text{fetch}}$  has changed pc in the previous step. Because of this, it is not difficult to see that for all  $S' \in \mathcal{S}'$ :

$$tip(S') \Rightarrow cycle^{4}(S') \upharpoonright M = O_{\mathsf{postp}}(O_{\mathsf{exec}}(O_{\mathsf{prep}}(O_{\mathsf{fetch}}(S' \upharpoonright (M' \setminus M'_{\mathsf{plc}}))))) \upharpoonright M . \tag{5}$$

We have that  $tip(S'_0)$  holds. Moreover, tip is preserved by the total processing of an instruction if there is a next instruction to be processed:

```

— if S'(\mathsf{M}_{\mathsf{prog}}[S'(\mathsf{pc})]) = a and S'(\mathsf{pc}) + 1 \le S'(\mathsf{pcbr}),

then tip(S') \Rightarrow tip(cycle^1(S'));

— if S'(\mathsf{M}_{\mathsf{prog}}[S'(\mathsf{pc})]) \in \{+a, -a\}, cycle^3(S')(\mathsf{isf}) = \mathsf{F} and S'(\mathsf{pc}) + 1 \le S'(\mathsf{pcbr}),

then tip(S') \Rightarrow tip(cycle^1(S'));

— if S'(\mathsf{M}_{\mathsf{prog}}[S'(\mathsf{pc})]) \in \{+a, -a\}, cycle^3(S')(\mathsf{isf}) = \mathsf{T} and S'(\mathsf{pc}) + 2 \le S'(\mathsf{pcbr}),

then tip(S') \Rightarrow tip(cycle^2(S'));

— if S'(\mathsf{M}_{\mathsf{prog}}[S'(\mathsf{pc})]) = \#k and S'(\mathsf{pc}) + k \le S'(\mathsf{pcbr}),

then tip(S') \Rightarrow tip(cycle^4(S')).

```

Let  $(p_i, S_i)$  be the (i+1)st element in the full path of  $(CT, S'_0 \upharpoonright (M' \setminus M'_{plc}))$  on H''. Then it is easy to prove by induction on i that

$$\begin{array}{ll} p_{4i+4} = CT & \text{if } S'_{4i+1}(\mathsf{rr}_{\mathsf{fetch}}) = \mathsf{T} \wedge S'_{4i+4}(\mathsf{rr}_{\mathsf{postp}}) = \mathsf{T} \;, \\ p_{4i+4} = \mathsf{S} & \text{if } S'_{4i+1}(\mathsf{rr}_{\mathsf{fetch}}) = \mathsf{T} \wedge S'_{4i+4}(\mathsf{rr}_{\mathsf{postp}}) = \mathsf{F} \;, \\ p_{4i+1} = \mathsf{D} & \text{if } S'_{4i+1}(\mathsf{rr}_{\mathsf{fetch}}) = \mathsf{F} \end{array} \tag{6}$$

(if  $4i + 4 < \|(CT, S'_0 \upharpoonright (M' \setminus M'_{\text{plc}}))\|_{H''}$  in case CT converges from  $S'_0 \upharpoonright (M' \setminus M'_{\text{plc}})$  on H''). Let  $(p'_i, S'_i)$  be the (i+1)st element in the full path of  $(CT', S'_0)$  on H'. Then it is

|                |       | · I · · · |       |       | I     |       | 9 .,  | , , . | , 11 9 | , - , ,, | -,, . |       |

|----------------|-------|-----------|-------|-------|-------|-------|-------|-------|--------|----------|-------|-------|

|                | 1     | 2         | 3     | 4     | 5     | 6     | 7     | 8     | 9      | 10       | 11    | 12    |

| a              | fetch | prep      | exec  | postp |       |       |       |       |        |          |       |       |

| +b             |       | fetch     | prep  | exec  | postp |       |       |       |        |          |       |       |

| #3             |       |           | fetch | prep  |       |       |       |       |        |          |       |       |

| $\overline{c}$ |       |           |       | fetch | prep  | exec  | postp |       |        |          |       |       |

| #2             |       |           |       |       | fetch | prep  | exec  | postp |        |          |       |       |

| d              |       |           |       |       |       | fetch |       |       |        |          |       |       |

| !              |       |           |       |       |       |       |       |       | fetch  | prep     | exec  | postp |

|                |       |           |       |       |       |       |       |       |        | fetch    |       |       |

Table 11. Pipelined instruction processing of a; +b; #3; c; #2; d; !

easy to prove by induction on i that

$$\begin{array}{ll} p'_{4i+4} = CT' & \text{if } tip(S_{4i}) \wedge S'_{4i+1}(\mathsf{rr}_{\mathsf{fetch}}) = \mathsf{T} \wedge S'_{4i+4}(\mathsf{rr}_{\mathsf{postp}}) = \mathsf{T} \; , \\ p'_{4i+4} = \mathsf{S} & \text{if } tip(S_{4i}) \wedge S'_{4i+1}(\mathsf{rr}_{\mathsf{fetch}}) = \mathsf{T} \wedge S'_{4i+4}(\mathsf{rr}_{\mathsf{postp}}) = \mathsf{F} \; , \\ p'_{4i+1} = \mathsf{D} & \text{if } tip(S_{4i}) \wedge S'_{4i+1}(\mathsf{rr}_{\mathsf{fetch}}) = \mathsf{F} \end{array} \tag{7}$$